近日,伟德国际1946源于英国集成电路科学与工程学院(产教融合学院)郭宇锋、蔡志匡教授团队与澳门大学模拟与混合信号超大规模集成电路国家重点实验室麦沛然教授团队合作的时钟芯片研究成果——A 16-MHz Crystal Oscillator with 17.5-μs Startup Time under 104-ppm-∆F Injection Using Automatic Phase-Error Correction(《一种基于相位差自动校正技术的快速启动16MHz晶体振荡器》)发表在集成电路领域国际顶级期刊IEEE Journal of Solid-State Circuits(《IEEE固态电路学报》)上。南邮王子轩副教授为该论文的第一作者,蔡志匡教授、麦沛然教授为共同通讯作者。

JSSC于1966年创刊,是集成电路领域公认影响力最大、发表难度最高的国际顶级学术期刊之一,也是中科院JCR分区中芯片设计领域唯一的一区期刊。这是伟德国际首次在JSSC上发表论文,也是江苏省属高校的首篇JSSC论文。

近年来,5G通信和物联网系统的广泛应用对时钟芯片的启动速度提出了较高要求。同频注入虽然是目前学术界公认的最有效的加速时钟启动的技术方案,但注入频偏容限过窄所导致的振荡器trim成本高、芯片良率低下一直是瓶颈问题,并阻碍该技术落地推广,始终无法实现商用。

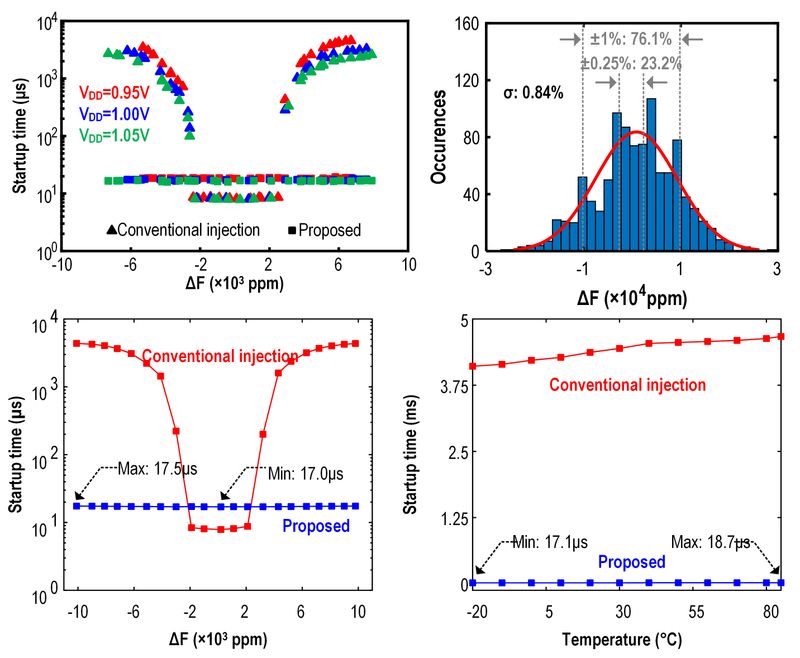

针对以上问题,团队提出一种基于相位误差自动校准的单边注入技术,引入负反馈对注入信号相位实时校准,从根本上克服了注入频偏对启动速度的影响。研究团队基于40纳米CMOS工艺完成了芯片的原型开发,实验结果表明,在注入频偏为±1%的范围内,时钟启动时间均小于19μs,突破了注入频偏的常规容限(5000ppm)。多样片(30pcs)测试结果显示,在0.95~1.05V电压范围内,采用单边注入技术的有效样片数量比传统注入技术高69%。团队提出的单边注入技术显著提升了电路鲁棒性和芯片良率,对推动注入技术的落地应用和快启动时钟芯片的商用进程具有重要意义。

该项研究同时得到了国家重点研发计划和国家自然科学基金的资助。

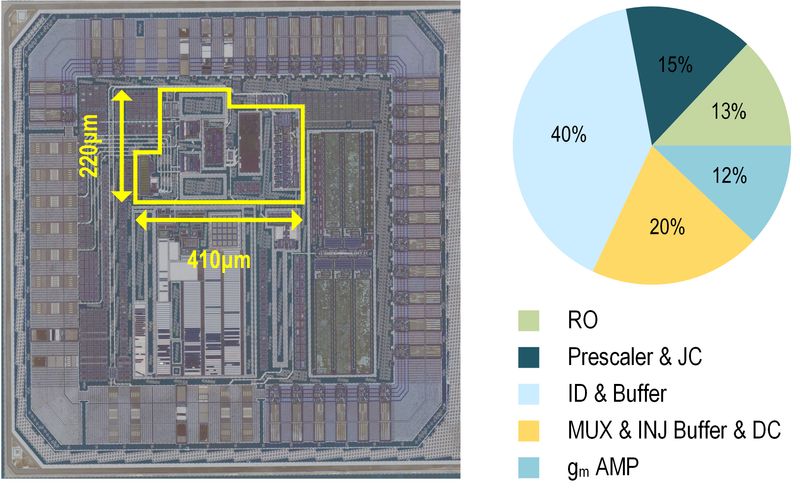

时钟芯片显微照片及能耗解析

时钟芯片快启动及高鲁棒性测试结果

论文链接:https://ieeexplore.ieee.org/document/10520270

(撰稿:王子轩 初审:戴修斌、蔡志匡 编辑:王存宏 审核:张丰)