2月20日,伟德国际集成电路科学与工程学院(产教融合学院)郭宇锋教授、蔡志匡教授团队在集成电路设计领域取得新进展,研发了一款基于相位误差自动校正技术的快速启动晶体振荡器芯片,该款芯片实现了大频偏注入条件下的快速启动,突破了对注入信号频率精度的严格限制,相关成果以“A 16MHz XO with 17.5μs Start-Up Time under 104ppm-∆F Injection Using Automatic Phase-Error Correction Technique”为题发表在第70届International Solid State Circuits Conference(ISSCC)上,并入选会议Demo演示(占比约20%)。该会议是集成电路设计领域的最高级别学术会议,素有“集成电路领域的奥林匹克”之称。该篇论文的发表,标志着伟德国际1946源于英国成为国内首家在ISSCC会议发表论文的省属高校。

晶体振荡器的启动时间影响系统的数据收发时间间隔,对于采用占空比工作模式的系统功耗具有决定性作用。随着物联网设备的飞速发展与低功耗应用场景的普及,快速启动晶体振荡器的作用至关重要。针对高频晶体振荡器启动时间及注入效率问题,团队提出一种基于相位误差自动校正技术的快速启动高频晶体振荡器芯片架构。该款芯片沿用目前效率最高的能量注入启动技术,首次提出相位误差自动校正概念,并首次在高频晶体振荡器设计中应用单端能量注入技术。其内部电路在对高频晶体进行能量注入的同时,检测注入信号与晶体振荡信号之间的相位误差并自动校正。经流片测试验证,在104ppm的大频偏注入条件下,该款芯片的实测启动时间为17.5μs,将该条件下的启动时间缩短249倍。与传统双端能量注入技术相比,其启动时间几乎不随注入频率误差波动(偏差仅为1.27%)。

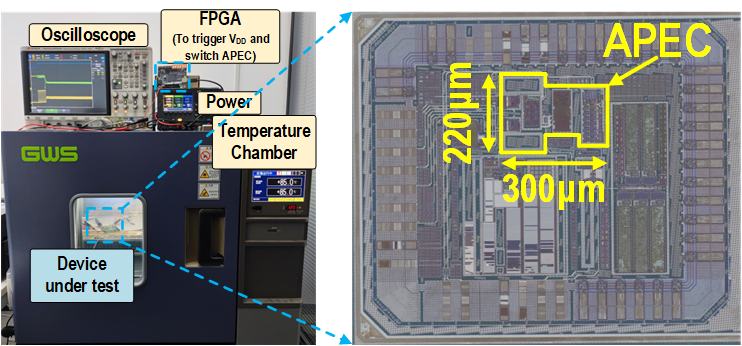

2月20日下午,集成电路科学与工程学院(产教融合学院)硕士研究生王鑫同学在ISSCC会场发表演讲介绍该款芯片,全球产业界及学术界数百位同行专家到场,并对团队的该项工作给予很高评价。当晚,集成电路科学与工程学院王子轩副教授主持该款芯片的现场功能演示及原理阐述,现场百余人对该款芯片进行深入探讨,并对本项工作的未来进展提出宝贵意见和建议。

该工作得到国家重点研发计划《片上低功耗高精度时钟系统研究》的资助。

基于相位误差自动校正技术的快速启动晶体振荡器芯片

会场演讲及Demo演示

(撰稿:王子轩 初审:蔡志匡、戴修斌 编辑:王存宏 审核:张丰)